Multi-level gate circuits

- 如何決定 level 數:

- Gate input number & Delay determine level

- Factoring to accomplish different level

- AND-OR: 2-level SOP

- OR-AND: 2-level POS

- OR-AND-OR: 3-level circuit of AND and OR → no particular ordering

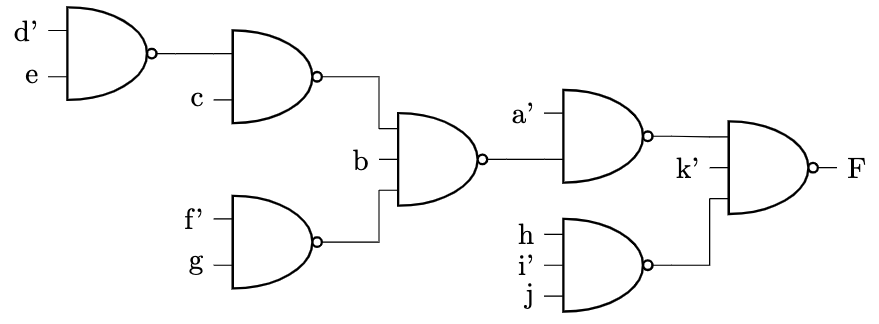

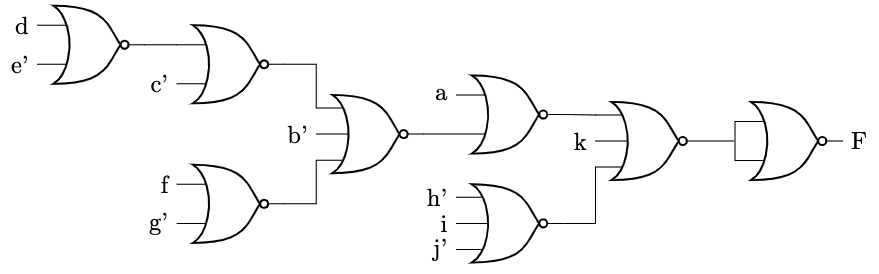

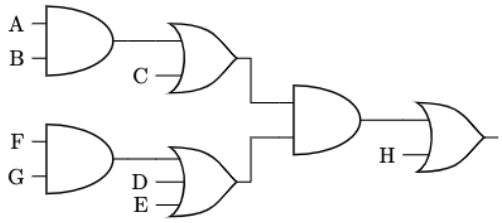

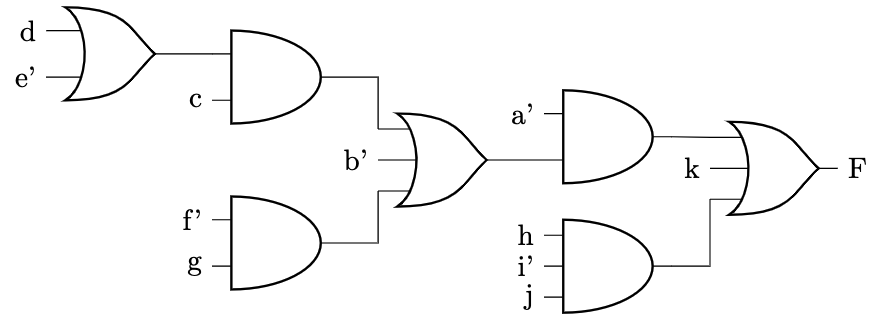

- 4 level gates:

- 3 level gates: (case fan out)

- Factoring 可變成 4-level

- Factoring 可變成 4-level

- level & gate & gate inputs 的關係會隨之變化,可根據電路設計的需求改變

- 範例:

- 範例:

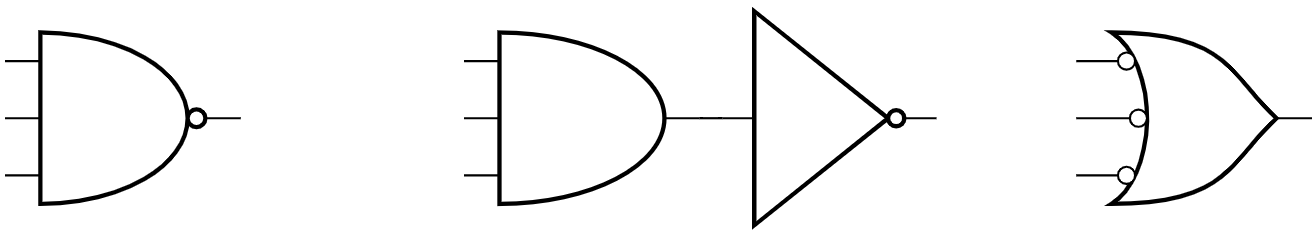

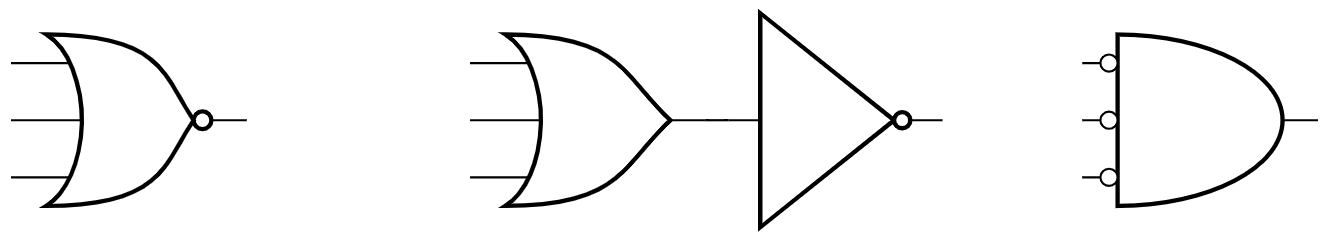

NAND and NOR gates

NAND

- 符號

- 真值表

- 布林表達式:

NOR

- 符號

- 真值表

- 布林表達式:

Functionally Complete Sets of Gates

- 定義:當所有的布林式皆可以被這組邏輯閘組合而成,則這組邏輯閘為 Functionally Complete

Majority Gate and Minority Gate

- 真值表

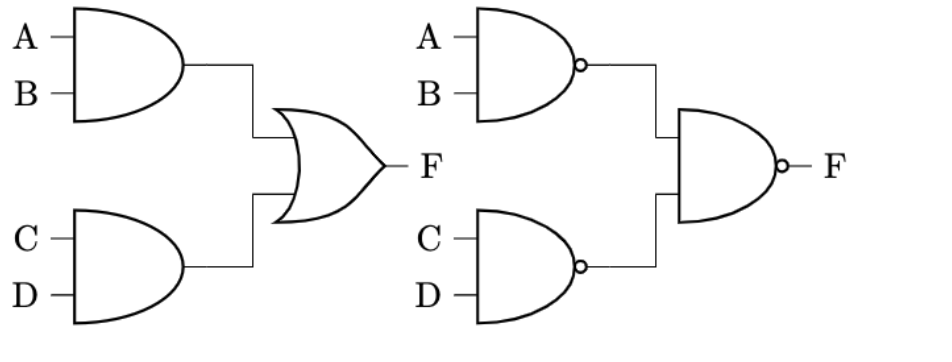

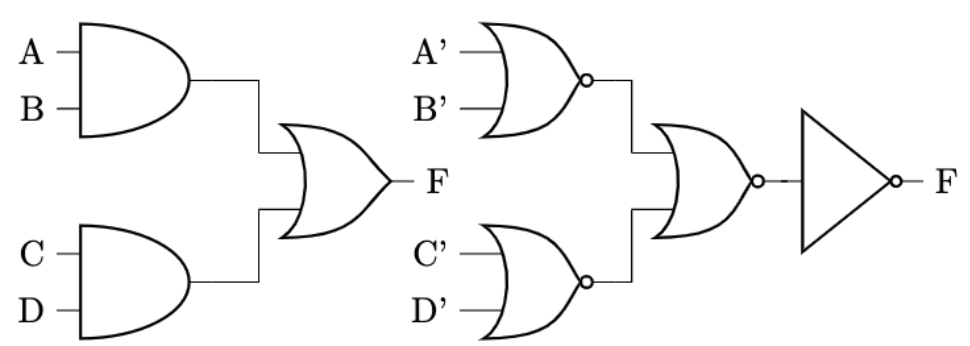

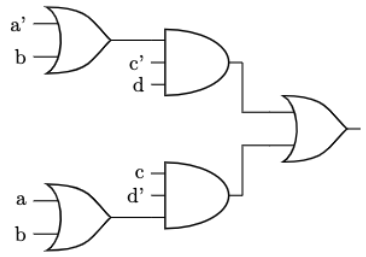

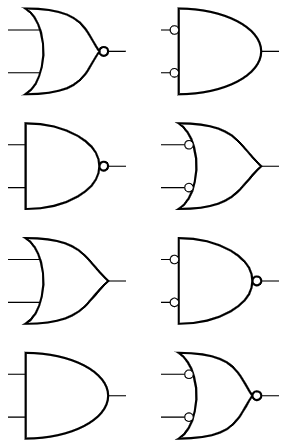

2-level NAND and NOR gates

DeMorgon’s Law

- 等效邏輯閘:

-

-

Multi-level NAND and NOR circuits

- Multi-level NAND and NOR circuits

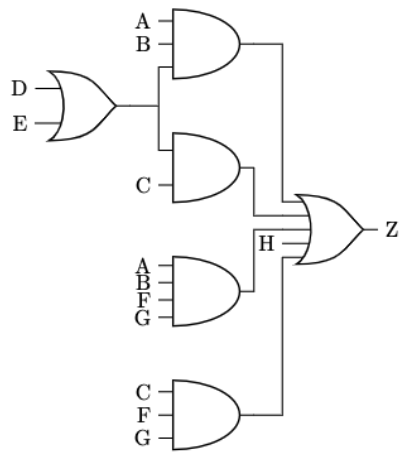

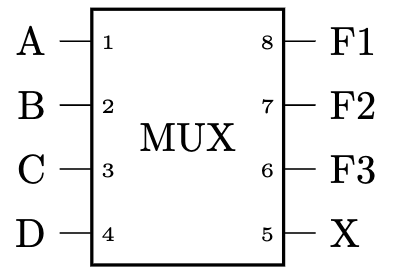

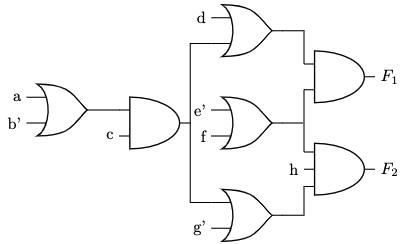

Multi-output circuit realization

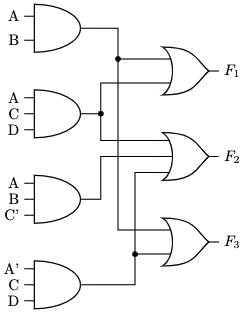

- 實際一個多工器(multiplexer)內的電路實現,可以用 fan out 的方式達到最佳化。

- 整體最佳不一定代表個別都為最佳。

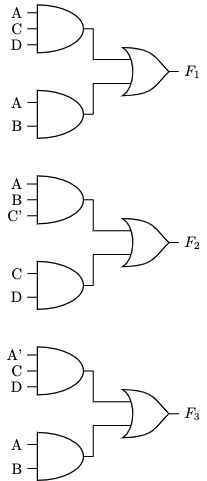

- 實作1:

- 實作2:

- 實作3:

- 使上面兩式共用

- 實作4:

- 不 combine 各自做最佳化

多輸出電路的基本質函項

- 參考實作3,若基本質函項可通過多工器中其他的輸入共用的話,則對多輸出電路而言並非基本質函項(Essential prime terms)。

- 參考實作4,皆為基本質函項。

- 一般而言,不會為了共享而把基本質函項拆開。

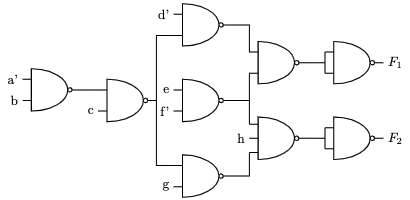

和項共用(Shared by sum terms)

- 真值表

- k-map

- Sum terms 也可以 share

- Multi-output circuits 也可以只用 表示

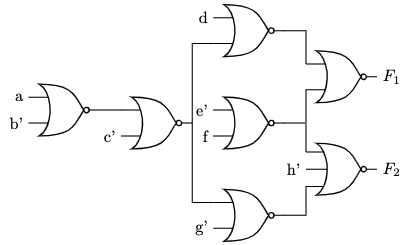

Multi-Output NAND/NOR circuits

- 範例

-